# LMX2434SLE EVALUATION BOARD OPERATING INSTRUCTIONS

# National Semiconductor Corporation

Wireless Communications, RF Products Group 2900 Semiconductor Dr. M/S E-170 Santa Clara, CA, 95052-8090

LMX2434SLEFPEBI Rev 05.12.06

# **Table of Contents**

| 1.0   | General Description                                         | . 1 |

|-------|-------------------------------------------------------------|-----|

| 1.1   | Quick Start                                                 |     |

| 1.1.1 | Recommended Test Equipment                                  | 1   |

| 1.1.2 | Connection And Setup                                        |     |

| 2.0   | Measurement Considerations                                  | 3   |

| 2.1   | Phase Noise Measurement Using A Spectrum Analyzer           | 3   |

| 2.2   | Loop Filter Bandwidth Measurement Using A Spectrum Analyzer | 4   |

| 2.3   | Reference Spur Measurement Using A Spectrum Analyzer        | 4   |

| 2.4   | Lock Time Measurement Using A Modulation Domain Analyzer    | 5   |

| 2.5   | Lock Time Measurement Using A Spectrum Analyzer             |     |

| 3.0   | Evaluation Board Configuration                              | 7   |

| 3.1   | RF PLL Loop Filter Parameters                               |     |

| 3.2   | IF PLL Loop Filter Parameters                               |     |

| 4.0   | Typical Performance Measurements                            |     |

| 4.1   | RF PLL Typical Performance Measurements                     | 9   |

| 4.2   | IF PLL Typical Performance Measurements                     | 13  |

|       | NDIX A: LMX2434SLE Evaluation Board Schematic               |     |

| APPE  | NDIX B: LMX2434SLE Evaluation Board – Board Layout          | 18  |

|       | NDIX C: LMX2434SLE Evaluation Board – Bill Of Materials     |     |

| APPE  | NDIX D: LMX2434SLE Evaluation Board – Build Diagram         | 21  |

| APPE  | NDIX E: LMX2434SLE How To Setup The Code Loader Software    | 22  |

#### 1.0 General Description

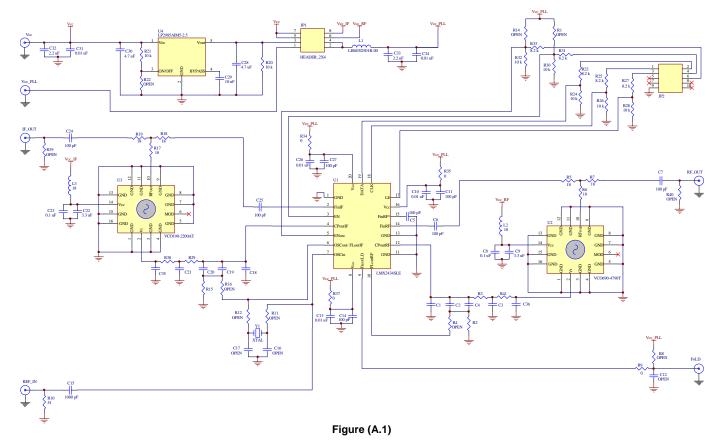

The LMX2434SLE Evaluation Board simplifies evaluation of the LMX2434SLE 5.0 GHz/2.5 GHz PLLatinum<sup>™</sup> dual frequency synthesizer. The board enables all performance measurements with no additional support circuitry.

The evaluation board consists of a LMX2434SLE device, RF and IF VCO modules, and RF and IF loop filters built by discrete components. The SMA flange mount connectors are provided for external reference input, RF and IF VCO outputs, and the power and grounding connection. A cable assembly is bundled with the evaluation board for connecting to a PC through the parallel printer port. By means of MICROWIRE<sup>™</sup> serial port emulation, the Code Loader software included can be run on a PC to facilitate the LMX2434SLE internal register programming for the evaluation and measurement.

## 1.1 Quick Start

The LMX2434SLE Evaluation Board is fully assembled and factory tested. Follow the instructions below to set up the hardware platform for the measurement of interest.

#### 1.1.1 <u>Recommended Test Equipment</u>

- Spectrum analyzer with operating frequency range > 5.0 GHz

- DC power supply with adjustable voltage outputs

- 10 MHz signal source/generator. A high quality TCXO is the preferred signal source. Alternatively, the 10 MHz (0 dBm) reference output from the rear panel of the spectrum analyzer may be used.

#### 1.1.2 Connection And Setup

- Connect the RF\_OUT/IF\_OUT output port to the input of the spectrum analyzer for phase noise and reference spur measurement or to the input of the modulation domain analyzer for lock time measurement.

- 2. Connect a 10 MHz reference oscillator to the REF\_IN input port. A high quality reference source such as a TCXO is preferred to achieve an accurate and low noise measurement. Depending on the reference source used, the 51Ω terminating resistor, designated R10, can be removed when appropriate. Alternatively, connect a signal generator to the REF\_IN input port and set the output frequency to 10 MHz. Keep the 51Ω resistor if the signal generator is used. Another option is to use the 10 MHz reference output from the rear panel of the spectrum analyzer.

- Plug the DB25 connector end of the cable assembly to the parallel port of the PC. Connect the other end of the cable to the on-board 10 Pin Header, JP2. Refer to Appendix E for more details. Alternatively, refer to the <u>Code Loader Operating</u> <u>Instructions</u> from National Semiconductor's Wireless Communications website: <u>wireless.national.com</u>.

- 4. Verify that three jumper blocks are in place so that the RF and IF sides as well as their corresponding VCOs have power to them. Refer to the schematic in Appendix A for proper placement of the jumper blocks.

- 5. Turn the DC power supply ON and adjust the voltage output to 5.0V. Turn the DC power supply OFF.

- Connect the DC power supply output to the V<sub>cc</sub> port of the evaluation board. Turn the DC power supply ON.

- 7. Run the Code Loader software for LMX2434SLE register programming. Ensure proper port setup, and that the frequency of the reference source on the Code Loader matches that actually used for the board. Refer to Appendix E for more details.

#### 2.0 Measurement Considerations

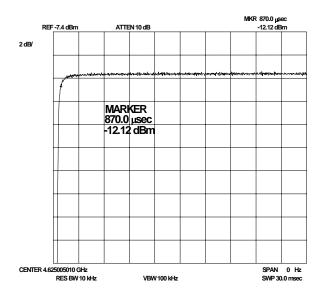

#### 2.1 Phase Noise Measurement Using A Spectrum Analyzer

The phase noise characteristics of the PLL can be measured on a spectrum analyzer or a phase noise test set. The spectrum analyzer test technique is described here. Phase noise is measured in units of dBc/Hz. In this evaluation, the phase noise is measured at 1 kHz offset from the output signal. For accurate close-in phase noise measurements, the offset frequency selected should be inside the loop bandwidth on the flat portion of the curve. For integrated phase noise measurements a phase noise analyzer is recommended.

The Code Loader software is used to set the desired frequency and to program the LMX2434SLE device. Refer to Appendix E for more details. For phase noise measurements at fixed offset frequencies, use an analyzer with a noise floor below the level of measurement interest. Since they are more readily available, below is an explanation of this test technique using a spectrum analyzer.

Tune the spectrum analyzer to the desired center frequency with the span adjusted to include the appropriate offset frequency. Using the delta marker, the difference between the carrier and the noise level at the desired offset frequency is measured. The video averaging feature of the spectrum analyzer should used to better determine the noise level.

The phase noise is a 1 Hz normalized bandwidth measurement expressed in dBc/Hz. Most modern spectrum analyzers have a feature that automatically normalizes the phase noise measurements to a 1 Hz bandwidth. This feature gives greater measurement accuracy. For spectrum analyzers without this feature, the normalized phase noise is equal to the noise level relative to the carrier minus 10 \* log10 [Resolution Bandwidth]. This formula does not take into account any errors from the spectrum analyzer.

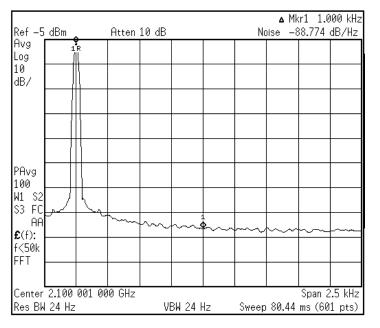

#### 2.2 Loop Filter Bandwidth Measurement Using A Spectrum Analyzer

The loop bandwidth is the bandwidth of the closed loop PLL system. It is, by definition, the frequency that makes the forward loop gain equal to zero. The spectrum analyzer span is set to view the characteristic rising, peaking, and falling of the phase noise. To measure the loop bandwidth is rather complex. It is simpler to measure the 0 dB bandwidth. Although, not exactly the same, the 0 dB bandwidth is a sufficient estimate of the loop filter bandwidth. The 0 dB bandwidth is defined as the frequency where the phase noise falls back to the level of the close-in value after rising to its peak value. The value measured is typically greater than the true loop filter bandwidth. For this evaluation, the 0 dB bandwidth is measured.

#### 2.3 Reference Spur Measurement Using A Spectrum Analyzer

The reference sidebands can be seen on a spectrum analyzer and are measured in dBc. The Code Loader software is used to set the desired frequency and to program the LMX2434SLE device. Refer to Appendix E for more details. The spectrum analyzer is set to the desired center frequency and the span is set to allow the reference sidebands to be viewed. For the LMX2434SLE device, the span can be set to 6 MHz during the RF or IF VCO measurements because their loop filter designs are based on a 2.5 MHz reference frequency. The spurious output is the difference between the level of the VCO output frequency tone and the level of the spur at an offset equal to the carrier frequency +/- the reference frequency. For a more accurate account of the device's spurious performance, the reference spurs across the VCO's frequency band should be determined. The worst-case spur is typically defined as the PLL's spur performance.

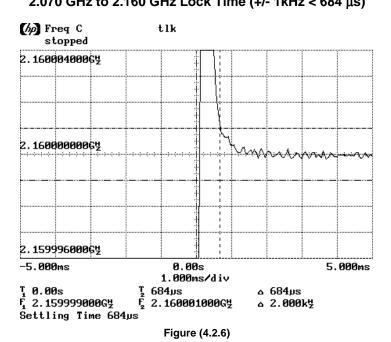

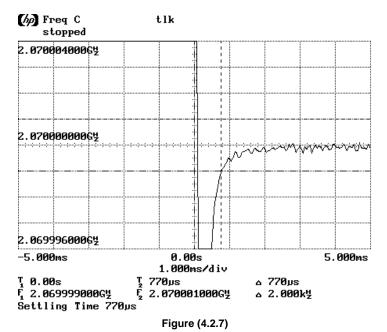

#### 2.4 Lock Time Measurement Using A Modulation Domain Analyzer

The modulation domain analyzer measures the switching speed, or lock time, using a frequency versus time plot. The modulation domain analyzer was used for the IF lock time measurement.

Set the center frequency of the modulation domain analyzer to the final (settling) frequency. Use a wide span allows viewing of the entire positive or negative switching waveform. Use a narrower span to evaluate the settling waveform within +/- 1 kHz. A trigger condition, typically a latch enable pulse, specifies the event that will cause the modulation domain analyzer to capture and display the measurement results. The lock time is the time difference between the point the frequency starts to change (T1), and the point the VCO frequency settles to within +/-1 kHz of the final value (T2), (i.e. lock time = T2 - T1).

Use the BurstMode tab of the CodeLoader software to program the device to toggle between a desired minimum and maximum frequency. It is necessary to include a sufficient delay, such as 100000, after each programming command. For more detail, refer to the BurstMode Tab section in the CodeLoader Operating Instructions from National Semiconductor's Wireless Communications website: wireless.national.com.

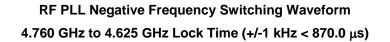

# 2.5 Lock Time Measurement Using A Spectrum Analyzer

The principle behind this is to use the spectrum analyzer as an FM demodulator to detect the frequency change over time when the PLL is switching between two frequencies. This method is called the Zero-Span mode. The idea is to convert the FM of the signal to amplitude variations and then measure these variations over time. The center frequency of the spectrum analyzer is first set to the final (settling) frequency. The frequency span and resolution bandwidth are both set to 10 kHz, and the video bandwidth is set to 100 kHz. The scale is set to 2 dB per division and the step size is set to 1 kHz per division. A filter response is displayed. The spectrum analyzer is tuned off the center frequency so that the slope of the tunable filter is used as an FM to AM converter. The linear section (slope) of the filter is at 5 kHz from the center frequency. The slope is approximately 1 dB/ 1 kHz. The frequency span is finally set to 0 Hz. A sweep time of 30 msec is used.

A x1 probe is used to connect the MICROWIRE to the external trigger on the rear panel of the spectrum analyzer. Using the Code Loader software, port address 'C1' is selected for the TRIGGER programming pin. The TRIGGER is then set to HIGH. Using the Burst Mode menu of the software, a macro is created to program the LMX2434SLE device to switch between the maximum and minimum frequency alternately over time. It is necessary to include a sufficient delay, such as 1000000, after each programming command. Refer to the Burst Mode Tab section in the <u>Code Loader Operating Instructions</u> from National Semiconductor's Wireless Communications website: <u>wireless.national.com</u>. The lock time is the time difference between the point the frequency starts to change (T<sub>1</sub>), and the point the PLL frequency settles within +/- 1 kHz range (T<sub>2</sub>), i.e. lock time = T<sub>2</sub> - T<sub>1</sub>. The single sweep feature of the spectrum analyzer can be used to capture the trace. (+/- 1 kHz tolerance corresponds to +/- 1 dB from the settling frequency).

Due to a maximum frequency range specification of 2.5GHz, the modulation domain analyzer cannot be used for the RF lock time measurement. Do to component tolerances, the maximum of some Vail 690-4700T VCOs used will not reach 4760 MHz with a tuning voltage of 2.0V and/or used will not reach 4625 MHz with a tuning voltage of 0.5V. The 2.0V is 0.5V below the 2.5V supply rail and 0.5V is above the ground rail, which is the delta specification in the datasheet. Also, Figure 4.1.6 and 4.1.7 shows lock times to and from 4625 and 4760 MHz. On instances where VCO does not reach these frequencies, use 4645 and/or 4740 MHz frequency. Other than the frequency the waveform should be the same as shown in Figures 4.1.6 and 4.1.7.

# 3.0 Evaluation Board Configuration

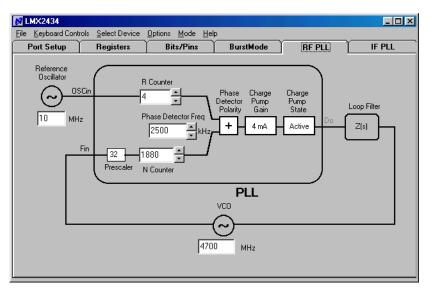

**RF PLL Loop Filter Parameters**

3.1

# $K_{0}$

| Settings For Operation                         |                  |  |  |

|------------------------------------------------|------------------|--|--|

| Charge Pump Gain<br>(Kø)                       | 4 mA (HIGH Gain) |  |  |

| Comparison<br>Frequency (f <sub>compRF</sub> ) | 2500 kHz         |  |  |

| Output Frequency<br>(f <sub>FinRF</sub> )      | 4645 - 4740 MHz  |  |  |

| VCO Supply                                     | 5.0V             |  |  |

| Other Information                              |                  |  |  |

| VCO Used                                       | VARI-L           |  |  |

|                                                | VCO690-4790T     |  |  |

| VCO Gain                                       | 94 MHz/V         |  |  |

| VCO Input<br>Capacitance                       | 12 pF            |  |  |

Figure (3.1)

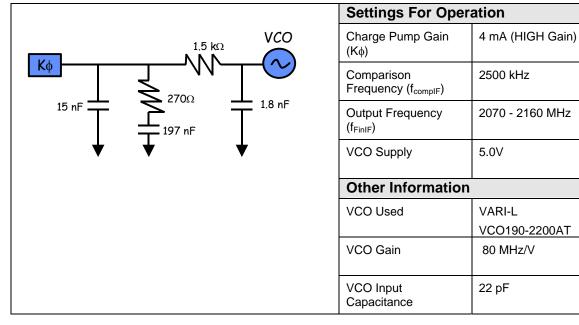

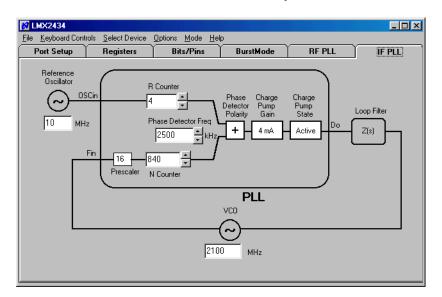

# 3.2 IF PLL Loop Filter Parameters

Figure (3.2)

#### 4.0 Typical Performance Measurements

The LMX2434SLE Evaluation Board has been tested to meet the typical performance criteria as shown below:

#### **Evaluation Conditions:**

| V <sub>cc</sub> Operating Voltage | 2.50V           |

|-----------------------------------|-----------------|

| TCXO Frequency                    | 10 MHz          |

| RF VCO Tuning Range               | 4645 - 4740 MHz |

| RF Comparison Frequency           | 2500 kHz        |

| IF VCO Tuning Range               | 2070 - 2160 MHz |

| IF Comparison Frequency           | 2500 kHz        |

#### **Typical Performance Criteria:**

| RF PLL Phase Noise    | < -80 dBc/Hz At 1 kHz Offset                       |

|-----------------------|----------------------------------------------------|

| RF PLL Reference Spur | < -75 dBc At 2500 kHz Offset                       |

| RF PLL Lock Time      | < 900 $\mu$ s (Within +/- 1kHz Settling Frequency) |

| IF PLL Phase Noise    | < -86 dBc/Hz At 1 kHz Offset                       |

| IF PLL Reference Spur | < -78 dBc At 2500 kHz Offset                       |

| IF PLL Lock Time      | < 1 ms (Within +/- 1kHz Settling Frequency)        |

#### Remark

Computer monitors and other lab equipment have been shown to cause noise spikes. If noise spikes are observed on the signal, try turning off the monitor or other equipment to verify that they are not the cause. In addition, noise may be getting onto the signal through the cable that connects to the parallel port of the computer.

#### 4.1 **RF PLL Typical Performance Measurements**

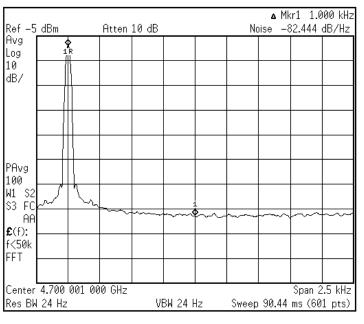

#### RF PLL Phase Noise at 4.700 GHz at 1.0 kHz Offset = -82.4 dBc/Hz

Figure (4.1.2)

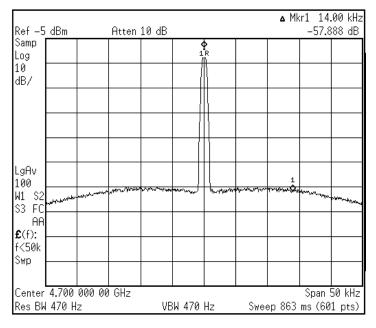

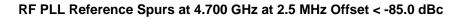

## RF PLL Reference Spurs at 4.645 GHz at 2.5 MHz Offset < -82.1 dBc

Figure (4.1.3)

| Figure | (4.1.4) |

|--------|---------|

|--------|---------|

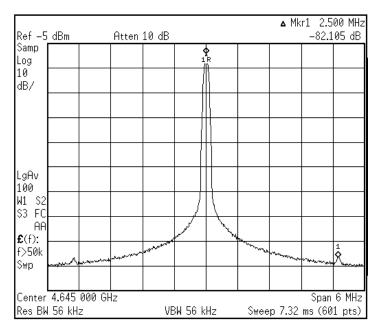

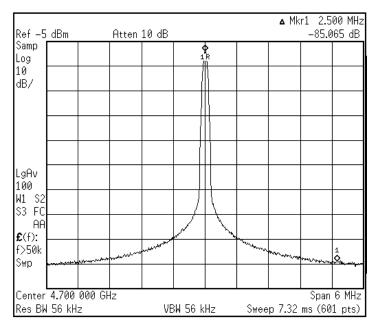

#### RF PLL Reference Spurs at 4.740 GHz at 2.5 MHz Offset < -83.9 dBc

Figure (4.1.5)

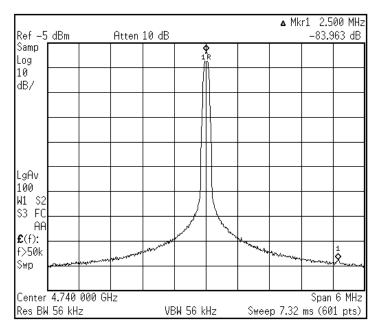

RF PLL Positive Frequency Switching Waveform 4.625 GHz to 4.760 GHz Lock Time (+/- 1kHz < 810.0 μs)

Figure (4.1.7)

#### 4.2 IF PLL Typical Performance Measurements

#### IF PLL Phase Noise at 2.100 GHz at 1.0 kHz Offset = -88.7 dBc/Hz

Figure (4.2.1)

IF PLL Loop Filter Bandwidth (≈16.00 kHz)

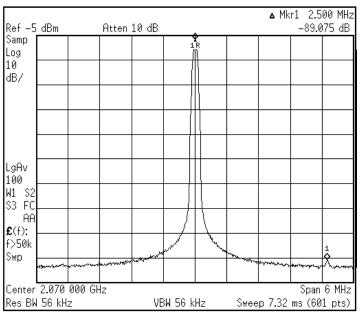

#### IF PLL Reference Spurs at 2.070 GHz at 2.5 MHz Offset < -89.0 dBc

Figure (4.2.3)

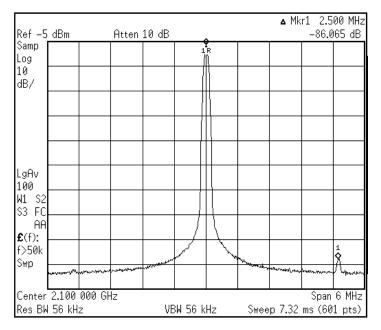

IF PLL Reference Spurs at 2.100 GHz at 2.5 MHz Offset < -86.0 dBc

Figure (4.2.4)

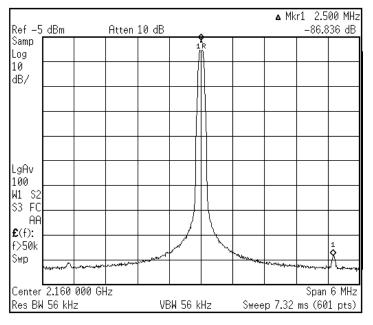

#### IF PLL Reference Spurs at 2.160 GHz at 2.5 MHz Offset < -86.8 dBc

Figure (4.2.5)

IF PLL Positive Lock Time Waveform Using HP53310A Modulation Domain Analyzer 2.070 GHz to 2.160 GHz Lock Time (+/- 1kHz < 684 μs)

IF PLL Negative Lock Time Waveform Using HP53310A Modulation Domain Analyzer

2.160 GHz to 2.070 GHz Lock Time (+/- 1kHz < 770 μs)

LMX2434SLE EVALUATION BOARD OPERATING INSTRUCTIONS

APPENDIX A: LMX2434SLE Evaluation Board Schematic

Note: 1. All jumpers are placed for the default configuration of the board (JP2 requires 3 jumpers: 3-4, 5-6, 7-8)

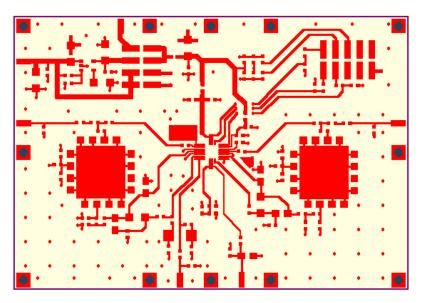

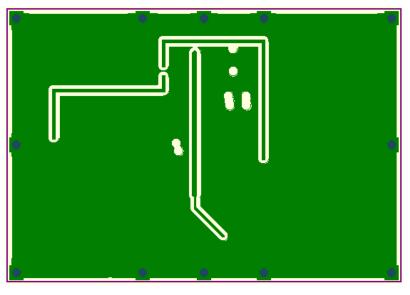

# **APPENDIX B:** LMX2434SLE Evaluation Board – Board Layout

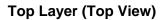

Top Layer

Figure (B.1)

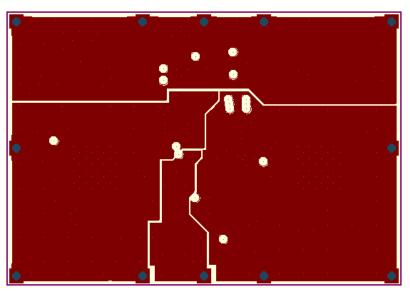

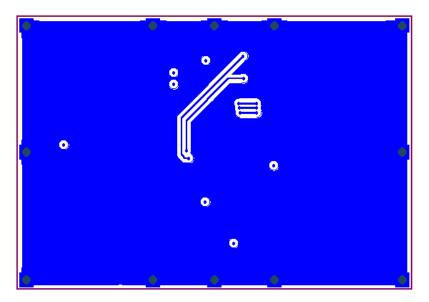

| Mi | dL | ay  | er1 |

|----|----|-----|-----|

|    |    | u y |     |

Figure (B.2)

# MidLayer2

Figure (B.3)

# **Bottom Layer**

Figure (B.4)

# **APPENDIX C:**

#### LMX2434SLE Evaluation Board – Bill Of Materials

| ITEM<br># | QTY | PART NUMBER         | DESCRIPTION                           | REFERENCE DESIGNATORS                                                                           | PREFERRED VENDOR       |  |

|-----------|-----|---------------------|---------------------------------------|-------------------------------------------------------------------------------------------------|------------------------|--|

| 1         | 18  | N/A                 | OPEN, NO COMPONENT                    | R1, R4, R8, R11, R12, R14, R16, R22,<br>R39, R40, C12, C16, C17, C35, C36,<br>Y1, Vcc_PLL, FoLD | N/A                    |  |

| 2         | 8   | C0603C101J5GAC      | CAP, 100 pF, CERAMIC, 5%, NP0, 0603   | C5, C6, C7, C11, C14, C24, C25, C27                                                             | KEMET                  |  |

| 3         | 1   | C0603C102J3GAC      | CAP, 1000 pF, CERAMIC, 5%, NP0, 0603  | C15                                                                                             | KEMET                  |  |

| 4         | 1   | C0603C122J5RAC      | CAP, 1200 pF, CERAMIC, 5%, X7R, 0603  | C3                                                                                              | KEMET                  |  |

| 5         | 1   | C0603C182J5RAC      | CAP, 1800 pF, CERAMIC, 5%, X7R, 0603  | C21                                                                                             | KEMET                  |  |

| 6         | 1   | C0805C822J5RAC      | CAP, 8200 pF, CERAMIC, 5%, X7R, 0805  | C1                                                                                              | KEMET                  |  |

| 7         | 5   | C0603C103J5RAC      | CAP, 0.01 μF, CERAMIC, 5%, X7R, 0603  | C10, C13, C26, C31, C34                                                                         | KEMET                  |  |

| 8         | 1   | C1206C103J3GAC      | CAP, 0.01 μF, CERAMIC, 5%, NP0, 1206  | C29                                                                                             | KEMET                  |  |

| 9         | 1   | C0805C223J5RAC      | CAP, 0.022 μF, CERAMIC, 5%, X7R, 0805 | C2                                                                                              | KEMET                  |  |

| 10        | 1   | C0805C153J5RAC      | CAP, 0.015 μF, CERAMIC, 5%, X7R, 0805 | C18                                                                                             | KEMET                  |  |

| 11        | 1   | C0805C473J5RAC      | CAP, 0.047 μF, CERAMIC, 5%, X7R, 0805 | C19                                                                                             | KEMET                  |  |

| 12        | 2   | C0603C104J3RAC      | CAP, 0.1 μF, CERAMIC, 5%, X7R, 0603   | C8, C23                                                                                         | KEMET                  |  |

| 13        | 1   | C1206C104J5RAC      | CAP, 0.1 μF, CERAMIC, 5%, X7R, 1206   | C4                                                                                              | KEMET                  |  |

| 14        | 1   | ECP-U1C154MA5       | CAP, 0.15 μF, FILM, 20%, 1206         | C20                                                                                             | PANASONIC              |  |

| 15        | 2   | C1206C225J8RAC      | CAP, 2.2 μF, CERAMIC, 5%, X7R, 1206   | C32, C33                                                                                        | KEMET                  |  |

| 16        | 2   | GMC21Y5V335Z16NE    | CAP, 3.3 μF, CERAMIC, 20%, Y5V, 0805  | C9, C22                                                                                         | CAL CHIP               |  |

| 17        | 2   | C1206C475K4PAC      | CAP, 4.7 μF, CERAMIC, 10%, X5R, 1206  | C28, C30                                                                                        | KEMET                  |  |

| 18        | 6   | CRCW0603000ZRT1     | RES, 0Ω, 0603                         | R9, R34, R35, R37, R38, R41                                                                     | VISHAY                 |  |

| 19        | 8   | CRCW0603180JRT1     | RES, 18Ω, 5%, 0603                    | R5, R6, R7, R17, R18, R19, L2, L3                                                               | VISHAY                 |  |

| 20        | 1   | CRCW0603510JRT1     | RES, 51Ω, 5%, 0603                    | R10                                                                                             | VISHAY                 |  |

| 21        | 1   | CRCW0603271JRT1     | RES, 270Ω, 5%, 0603                   | R15                                                                                             | VISHAY                 |  |

| 22        | 1   | CRCW0603561JRT1     | RES, 560Ω, 5%, 0603                   | R2                                                                                              | VISHAY                 |  |

| 23        | 1   | CRCW0603152JRT1     | RES, 1.5 kΩ, 5%, 0603                 | R29                                                                                             | VISHAY                 |  |

| 24        | 1   | CRCW0603222JRT1     | RES, 2.2 kΩ, 5%, 0603                 | R3                                                                                              | VISHAY                 |  |

| 25        | 5   | RMC 1/16 8.2K 1% R  | RES, 8.2 kΩ, 1%, 0603                 | R23, R25, R27, R31, R33                                                                         | SEI                    |  |

| 26        | 7   | RMC 1/16 10.0K 1% R | RES, 10 kΩ, 1%, 0603                  | R20, R21, R24, R26, R28, R30, R32                                                               | SEI                    |  |

| 27        | 1   | LI0603D301R-00      | FERRITE BEAD, 300Ω, 0603              | L1                                                                                              | STEWARD                |  |

| 28        | 4   | 5762SF              | CONNECTOR, SMA, 50 Ω                  | Vcc, RF_OUT, IF_OUT, REF_IN                                                                     | CDI                    |  |

| 29        | 3   | CCIJ255G            | SHUNT, 0.100" CENTER, CLOSED TOP      |                                                                                                 | COMM CON CONNECTORS    |  |

| 30        | 1   | HTSM3203-8G2        | HEADER, 8 PIN                         | JP1                                                                                             | COMM CON CONNECTORS    |  |

| 31        | 1   | HTSM3203-10G2       | HEADER, 10 PIN                        | JP2                                                                                             | COMM CON CONNECTORS    |  |

| 32        | 1   | LMX2434SLE          | IC, PLL                               | U1                                                                                              | NATIONAL SEMICONDUCTOR |  |

| 33        | 1   | LMX2434SLEEBPCB     | РСВ                                   | NATIONAL SEMICONDU                                                                              |                        |  |

| 34        | 1   | LP2985AIM5-2.5      | REGULATOR, SOT2-3                     | U4                                                                                              | NATIONAL SEMICONDUCTOR |  |

| 35        |     | VCO190-2200AT       | VCO                                   | U3 VARI-L                                                                                       |                        |  |

| 36        |     | VCO690-4790T        | VCO                                   | U2 VARI-L                                                                                       |                        |  |

| 37        |     | LMXOGTSP            | FRAME, 2.25" x 3.25"                  | LUX MANUFACTURING                                                                               |                        |  |

| 38        |     | OF12SHCA            | SCREW, 0-80x1/8                       |                                                                                                 | ORLANDER INC           |  |

| 39        |     | 2C18PPMZZ           | SCREW, 2-56x3/16, PHILIPS, PAN-HEAD   |                                                                                                 | ORLANDER INC           |  |

| 39        | 12  | LMX2434SLEF         |                                       |                                                                                                 | 20                     |  |

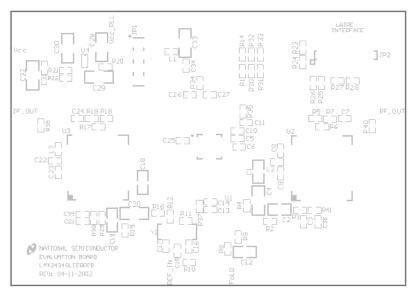

# **APPENDIX D:**

# LMX2434SLE Evaluation Board – Build Diagram

Figure (D.1)

# **Bottom Layer – No Components**

#### APPENDIX E:

#### LMX2434SLE How To Setup The Code Loader Software

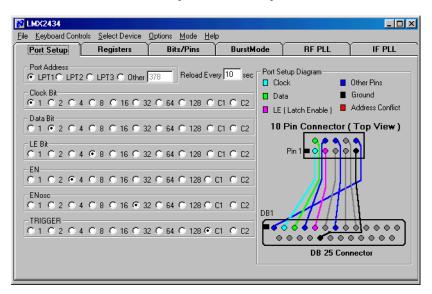

The port setup is necessary to tell the Code Loader program which signals to send to which locations on the computer parallel port. The proper setup for this part is shown below. The *Bits/Pins* page controls special functions in the PLL. For the LMX2434SLE, these special functions include the Timeout Counter bits, Power Control bits, and the operation of the EN, ENosc, and Ftest/LD pins.

#### **Proper Port Setup**

Figure (E.1)

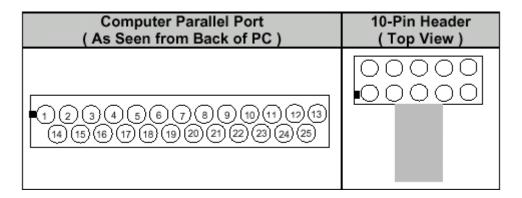

#### Port Setup And Corresponding PC Parallel Port And 10-Pin Header Configuration

| Port<br>Setup<br>Name | Port<br>Setup<br>Column | DB25 Connector Pin | 10-Pin Header Pin |

|-----------------------|-------------------------|--------------------|-------------------|

| 1                     | 1                       | DB2                | 1                 |

| 2                     | 2                       | DB3                | 2                 |

| 4                     | 3                       | DB4                | 4                 |

| 8                     | 4                       | DB5                | 3                 |

| 16                    | 5                       | DB6                | 5                 |

| 32                    | 6                       | DB7                | 6                 |

| 64                    | 7                       | DB8                | 7                 |

| 128                   | 8                       | DB9                | 8                 |

| C1                    | 9                       | DB1                | 10                |

| C2                    | 10                      | DB25               | Not Used          |

| N/A                   | N/A                     | 18 ( Ground )      | 9                 |

Figure (E.2)

# Pin 1 Position For PC Parallel Port And 10-Pin Header

Figure (E.3)

# Default Bits/Pins Setup

| M LMX2434     □ □ ×                                    |            |              |        |        |  |  |  |

|--------------------------------------------------------|------------|--------------|--------|--------|--|--|--|

| File Keyboard Controls Select Device Options Mode Help |            |              |        |        |  |  |  |

| Port Setup Registers                                   | Bits/Pins  | BurstMode    | RF PLL | IF PLL |  |  |  |

| RF_PD IF_TO RF_RST IF Power Controls                   | REF Cycles | Program Pins |        |        |  |  |  |

Figure (E.4)

**RF PLL Default Setup**

**IF PLL Default Setup**

Figure (E.6)

Figure (E.5)